010<sup>760</sup> & 54/7491A

8-BIT SHIFT REGISTER

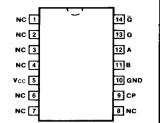

CONNECTION DIAGRAMS

PINOUT A

PINOUT B

# NC 1 14 Q 13 Q 13 Q NC 2 12 A 11 GND NC 5 10 B NC 6 9 CP NC 7 6 NC

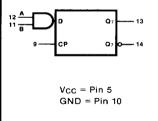

LOGIC SYMBOL

(Pinout A only)

# Datasheet.Te

**DESCRIPTION** — The '91 is a serial-in, serial-out, 8-bit shift register. It is composed of eight RS master/slave flip-flops, input gating and a clock driver. The register is capable of storing and transferring data at clock rates up to 18 MHz while maintaining a typical noise immunity level of 1.0 V.

ORDERING CODE: See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                                        | PKG<br>TYPE |  |  |

|--------------------|-----|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------|--|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{ C} \text{ to } +125^{\circ}\text{ C}$ |             |  |  |

| Plastic<br>DIP (P) | Α   | 7491APC                                                                                  |                                                                                                       | 9A          |  |  |

| Ceramic<br>DIP (D) | Α   | 7491ADC                                                                                  | 7491ADM                                                                                               | 6A          |  |  |

| Flatpak<br>(F)     | В   | 7491AFC                                                                                  | 7491AFM                                                                                               | 31          |  |  |

INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES | DESCRIPTION                            | <b>54/74 (U.L.)</b><br>HIGH/LOW |  |

|-----------|----------------------------------------|---------------------------------|--|

| A, B      | Serial Data Inputs                     | 1.0/1.0                         |  |

| CP        | Clock Pulse Input (Active Rising Edge) | 1.0/1.0                         |  |

| Q7        | Data Output                            | 10/10                           |  |

| ₫7        | Complementary Data Output              | 10/10                           |  |

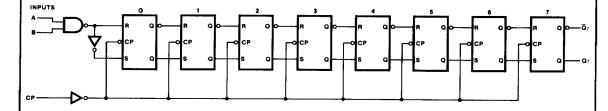

**FUNCTIONAL DESCRIPTION** — Single-rail data and input control are gated through inputs A and B and an internal inverter to form the complementary inputs to the first bit of the shift register. Drive for the internal common clock line is provided by an inverting clock driver. Each of the inputs (A, B, and CP) appear as only one TTL input load. The clock pulse inverter/driver causes these circuits to shift information to the output on the positive edge of an input clock pulse, thus enabling the shift register to be fully compatible with other edge-triggered synchronous functions.

#### **LOGIC DIAGRAM**

### TRUTH TABLE

|   | INI | PUTS | OUTPUT             |  |  |

|---|-----|------|--------------------|--|--|

|   |     | tn   | t <sub>n</sub> + 8 |  |  |

|   | Α   | В    | Q <sub>7</sub>     |  |  |

|   | L   | L    | L                  |  |  |

| I | L   | Н    | L                  |  |  |

| ı | Н   | L    | L                  |  |  |

| l | Н   | Н    | Н                  |  |  |

#### NOTES:

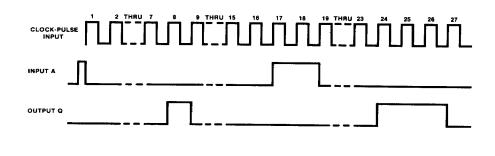

tn = Bit time before clock pulse.

$t_{n+8}$  = Bit time after eight clock pulses.

H = HIGH Voltage Level

L = LOW Voltage Level

#### TYPICAL INPUT/OUTPUT WAVEFORMS

# DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

| SYMBOL | PARAMETER            | 54/74 |         | UNITS | CONDITIONS |                        |

|--------|----------------------|-------|---------|-------|------------|------------------------|

|        |                      |       | Min Max |       |            |                        |

| lcc    | Power Supply Current | XM    |         | 50    |            |                        |

|        | XC XC                |       |         | 58    | l mA       | V <sub>CC</sub> = Max* |

<sup>\*</sup>Icc is measured after the eighth clock pulse with the output open and A and B inputs grounded

# AC CHARACTERISTICS: $V_{CC} = +5.0 \text{ V}$ , $T_A = +25^{\circ}\text{C}$ (See Section 3 for waveforms and load configurations)

|              |                                     | <b>54/74</b> C <sub>L</sub> = 15 pF R <sub>L</sub> = 400 Ω |          | UNITS | CONDITIONS     |

|--------------|-------------------------------------|------------------------------------------------------------|----------|-------|----------------|

| SYMBOL       | PARAMETER                           |                                                            |          |       |                |

|              |                                     | Min                                                        | Max      | 1     |                |

| fmax         | Maximum Shift Frequency             | 10                                                         |          | MHz   | Figs. 3-1, 3-8 |

| tpLH<br>tpHL | Propagation Delay<br>CP to Q7 or Q7 |                                                            | 40<br>40 | ns    | Figs. 3-1, 3-8 |

## AC OPERATING REQUIREMENTS: VCC +5.0 V, TA = +25°C

| SYMBOL             | PARAMETER                | 54/74 |     | UNITS | CONDITIONS |

|--------------------|--------------------------|-------|-----|-------|------------|

|                    | · Anameren               | Min   | Max | UNITS | CONDITIONS |

| t <sub>s</sub> (H) | Setup Time HIGH, D to CP | 25    |     | ns    | Fig. 3-6   |

| t <sub>h</sub> (H) | Hold Time HIGH, D to CP  | 0     |     | ns    | Fig. 3-6   |

| t <sub>s</sub> (L) | Setup Time LOW, D to CP  | 25    |     | ns    | Fig. 3-6   |

| t <sub>h</sub> (L) | Hold Time LOW, D to CP   | 0     |     | ns    | Fig. 3-6   |

| t <sub>w</sub> (H) | CP Pulse Width HIGH      | 25    |     | ns    | Fig. 3-8   |